Allocation of Physical Memory

- Contiguous allocation(연속할당)

- Noncontiguous allocation(불연속할당)

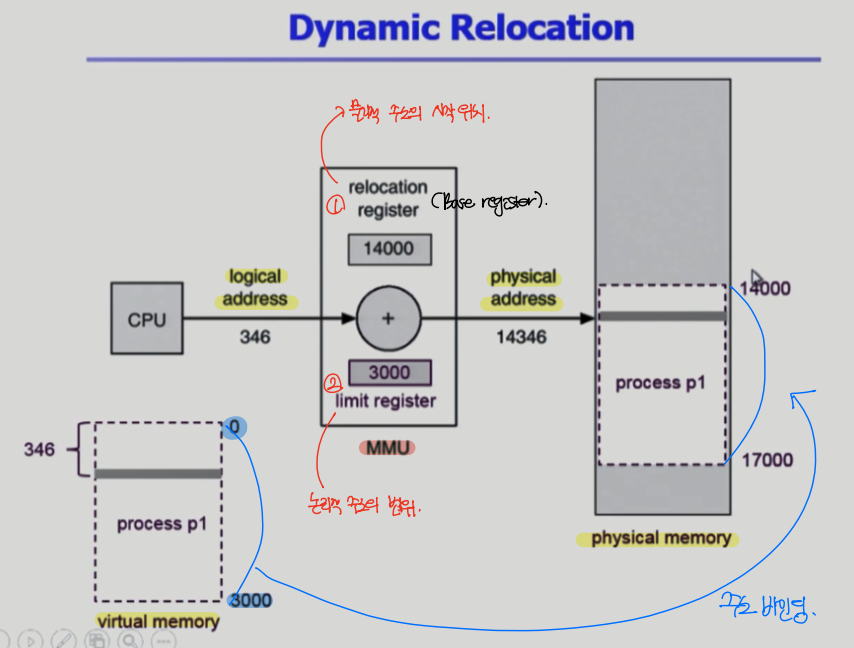

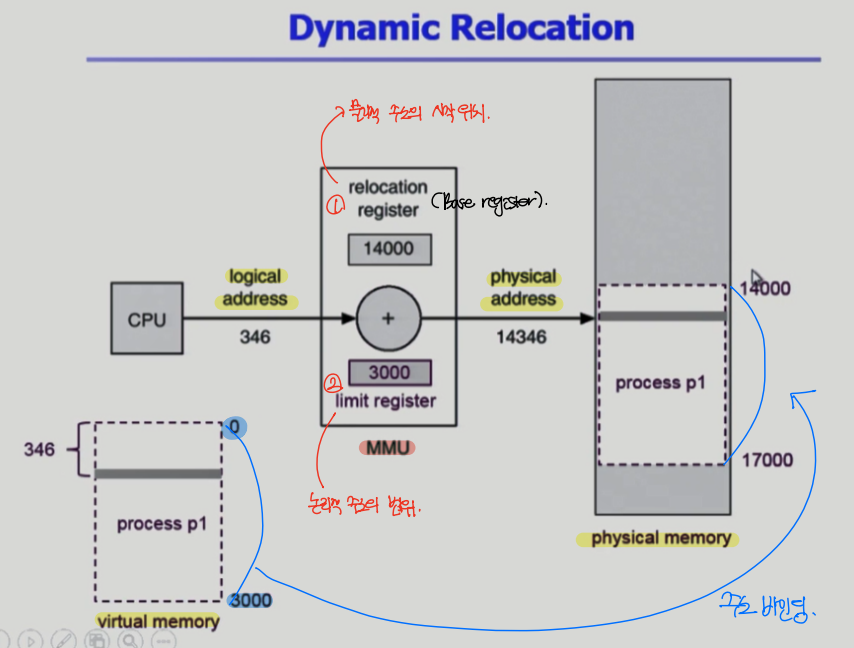

Contiguous allocation(연속할당)

Noncontiguous allocation(불연속할당)

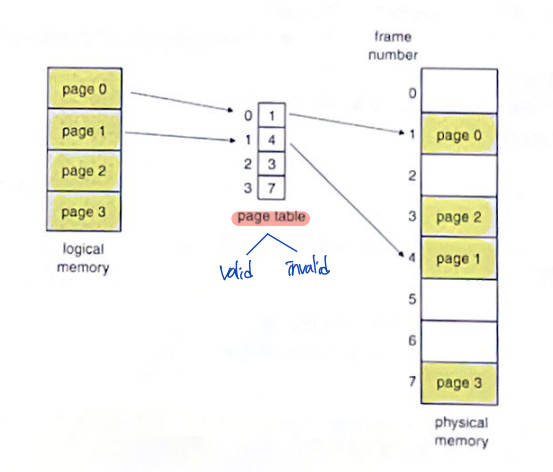

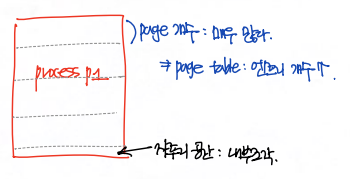

Paging

- Process의 logical memory를 동일한 사이즈의 page로 나눈다. --> logical memory의 내용이 page 단위로 noncontiguous(불연속)하게 저장된다.

- physical memory를 동일한 사이즈의 frame으로 나눈다. (page의 크기 = frame의 크기)

- page table: logical address --> physical address

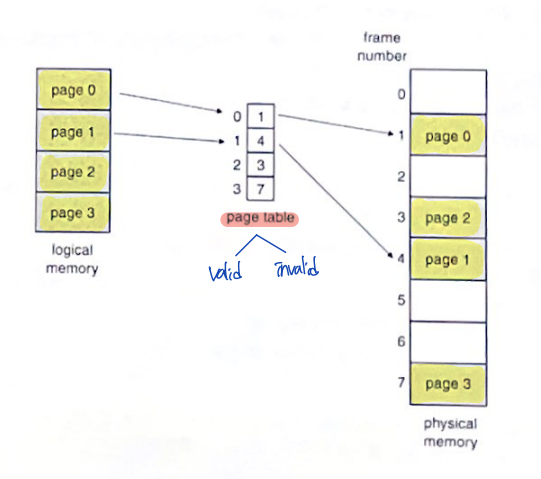

- page table -- valid/invalid: 일부는 backing storage(swap area)에, 일부는 physical memory 저장된다.

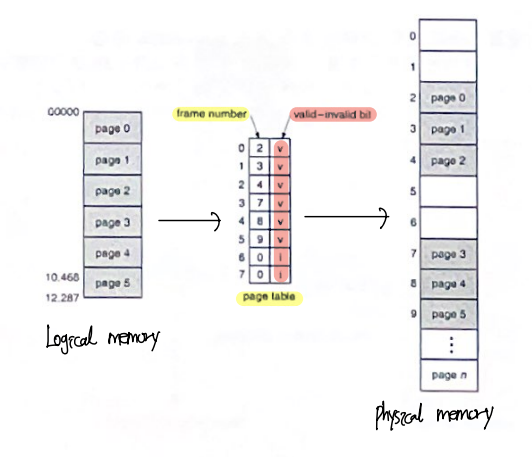

※ Page Table: valid-invalid bit

- valid: 해당 주소의 frame에 그 프로세스를 구성하는 유효한 내용이 있다: 접근 허용

- invalid: 해당 주소의 frame에 그 프로세스를 구성하는 유효한 내용이 없다: 접근 불허

- 프로세스가 그 주소 부분을 사용하지 않는 경우

- 해당 페이지가 메모리에 올라와 있지 않고, swap area에 있는 경우

- 외부조각(아무도 사용할 수 없는, 너무 작은 조각) 발생x: page 크기 = frame 크기 --> 아무에게도 할당받지 않을 수는 없다.

- 내부조각(할당 받았는데 사용되지 않는, 너무 큰 조각) 발생 가능

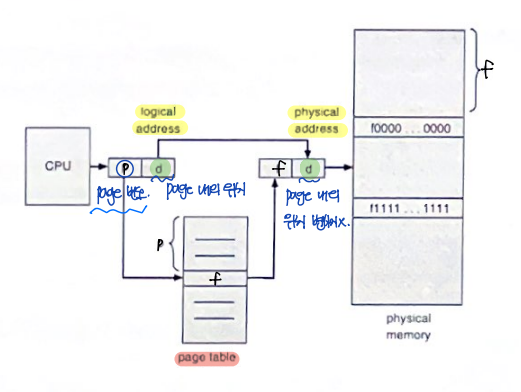

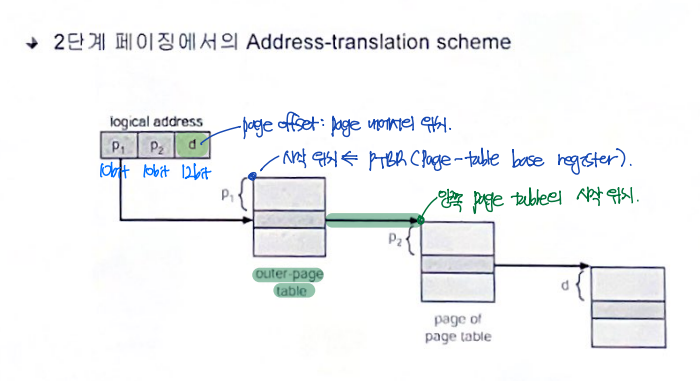

Address Transition Architecture: Logical address의 구성

- Page number(p): page 번호 --> Physical address로 넘어갈 때, 변경된다.

- Page offset(d): page 내의 위치 --> Physical address로 넘어갈 때, 변경되지 않는다.

Implementation of Page Table

- Page Table은 main memory 상주한다.

- PTBR(Page-Table Base Register): page table을 가리킴

- PTLR(Page-Table Length Register): page table 크기 보관

▷ Problem: 모든 메모리 접근 연산에는 2번의 memory access가 필요하다.

- page table 접근 1번, 실제 data/instruction 접근 1번

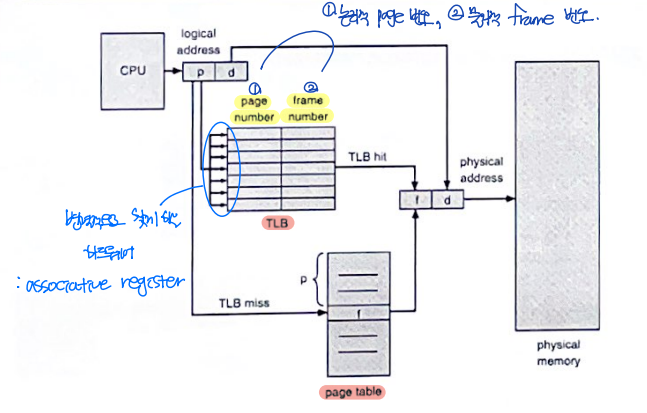

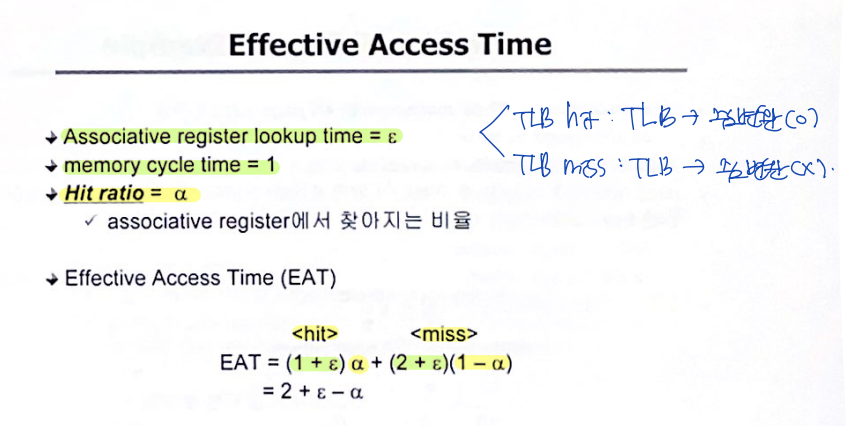

▷ Solution: TLB(Transition Look-aside Buffer) - 주소변환을 전담하는 캐시메모리

TLB

- associative register: TLB의 parallel search를 가능하게 하는 하드웨어

▶ Address translation

- page table 중 일부가, TLB(associative register)에 보관되어 있다.

- 만약 해당 page #가 TLB(associative register)에 보관되어 있는 경우, 곧바로 frame #를 얻는다.

- 그렇지 않은 경우, main memory에 있는 page table로부터 frame #를 얻는다.

- TLB: context switch 때 flush(remove old entries)

EAT(Effective Access Time)

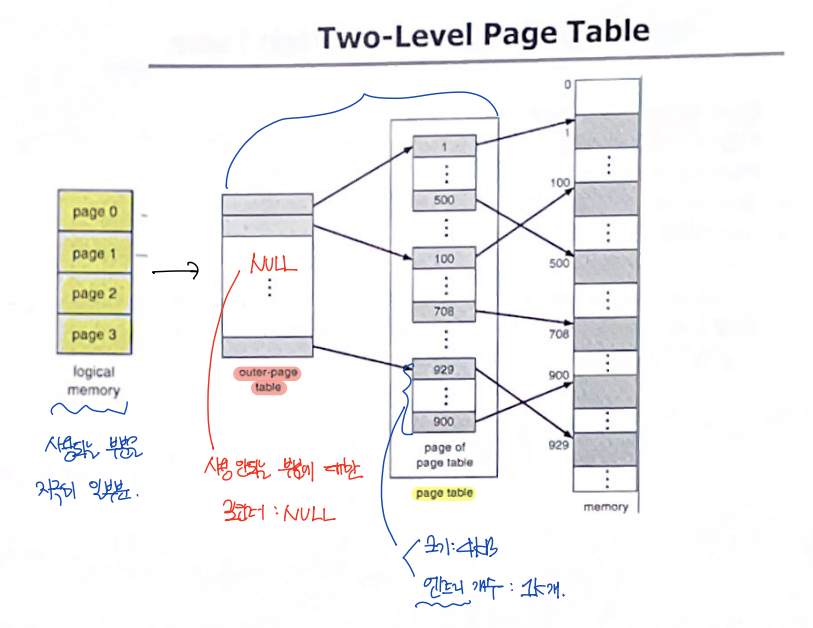

Two-Level Page Table

※ Page Table

- logical memory를 동일 크기의 page로 잘라서, physical memory에 빈 위치가 있으면 아무 곳에나 올릴 수 있다(불연속 할당).

- 당장 필요한 페이지만 physical memory에 올리고, 나머지는 swap area로 이동시킨다. --> 메모리의 효율적 사용

▷ Problem

- 32-bit address 사용 --> 2^32(4G)의 logical address space(논리적 주소공간)가 필요

- logical memory의 page 크기가 4K시, page table에는 1M개의 page table entry가 필요하다.

- 각 page table entry가 4B시, 프로세스당 4M의 page table이 필요하다.

- 그러나, 대부분의 프로그램은 4G의 logical address space(주소공간) 중 지극히 일부만을 사용하므로, page table 공간이 심하게 낭비된다.

▷ Solution

: page table 자체를 page로 구성한다: Two-Level Page Table

- 사용되지 않는 주소공간에 대한 outer page table의 엔트리 값 = NULL

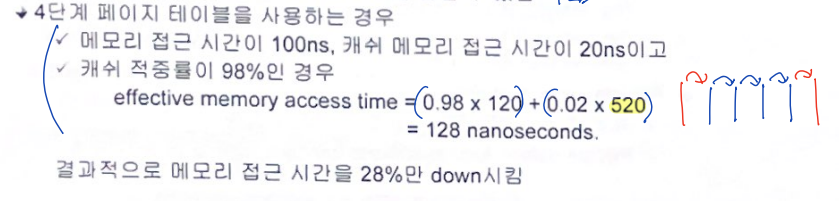

Multilevel Paging and Performance

- Logical address space(주소 공간)가 더 커지면, 다단계 페이지 테이블이 필요할 수 있다.

▷ Problem: 각 단계의 page table이 메모리에 존재하므로, logical address의 physical address 변환에 더 많은 메모리 접근이 필요해진다.

▷ Solution: TLB -- TLB 캐시메모리를 통해 메모리 접근 시간을 줄일 수 있다.

'운영체제' 카테고리의 다른 글

| [운영체제] KOCW 11.1 - Ch9: Virtual Memory (0) | 2023.06.10 |

|---|---|

| [운영체제] KOCW 10 - Ch8: Memory Management (0) | 2023.06.10 |

| [운영체제] KOCW 8 - Ch8: Memory Management (0) | 2023.06.09 |

| [운영체제] KOCW 7 - Ch7: Deadlock (0) | 2023.06.09 |

| [운영체제] KOCW 6.3 - Ch7: Deadlock (0) | 2023.06.09 |