A Pipelined Datapath

▶ Five Stages:

- IF: Instruction fetch.

- ID: Instruction decode & register file read.

- EX: Execution or address calculation.

- MEM: Data memory access.

- WB: Write back.

Single-Cycle Datapath

- Control Hazard: branch 여부에 따라 PC값이 달라진다.

- Branch (x) --> PC+4

- Branch (o) --> (PC+4) + offset - Data Hazard: Register file에서 서로 다른 instruction에 대한 WB과 ID가 동시에 일어나기 때문에 발생한다.

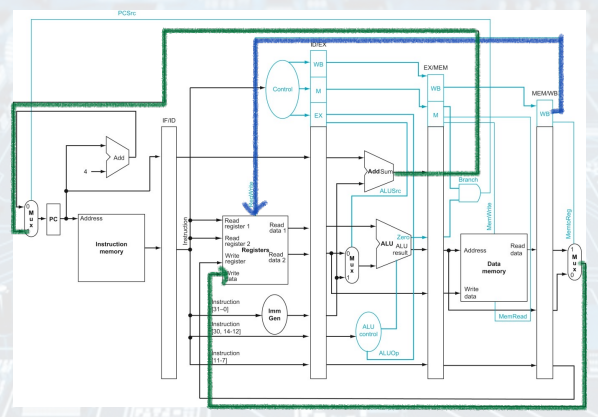

Pipeline Registers

: The value (instruction) must be saved in pipeline registers.

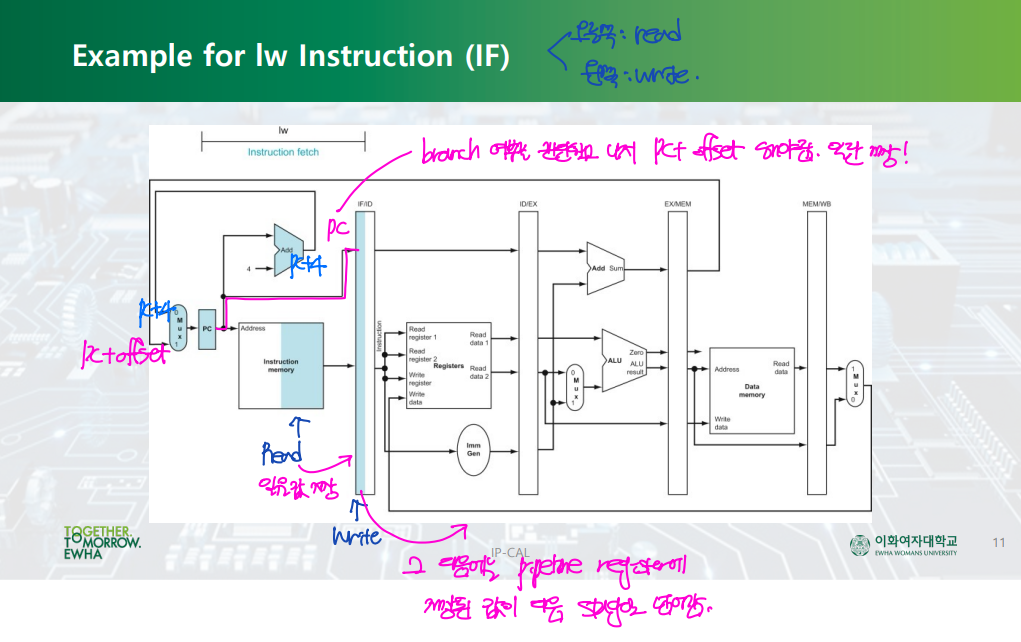

Example for lw Instruction

- PC가 가리키는 instruction memory 주소에서 instruction을 읽고, IF/ID pipeline register에 저장한다.

- PC --> PC+4 증가하고,

증가하기 전의 PC 값을 IF/ID pipeline register에 저장한다.

- IF/ID pipeline register에서 Read register, Write register 번호를 받아오고, Register file에서 Read data 값들을 읽는다.

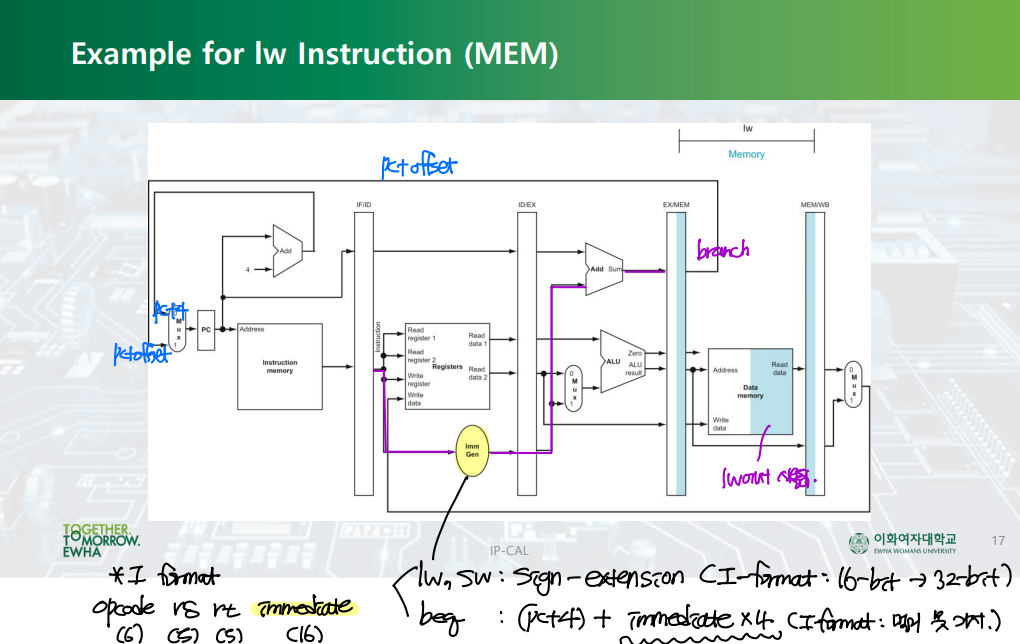

- ImmGen에서 immediate값을 sign-extension한다.

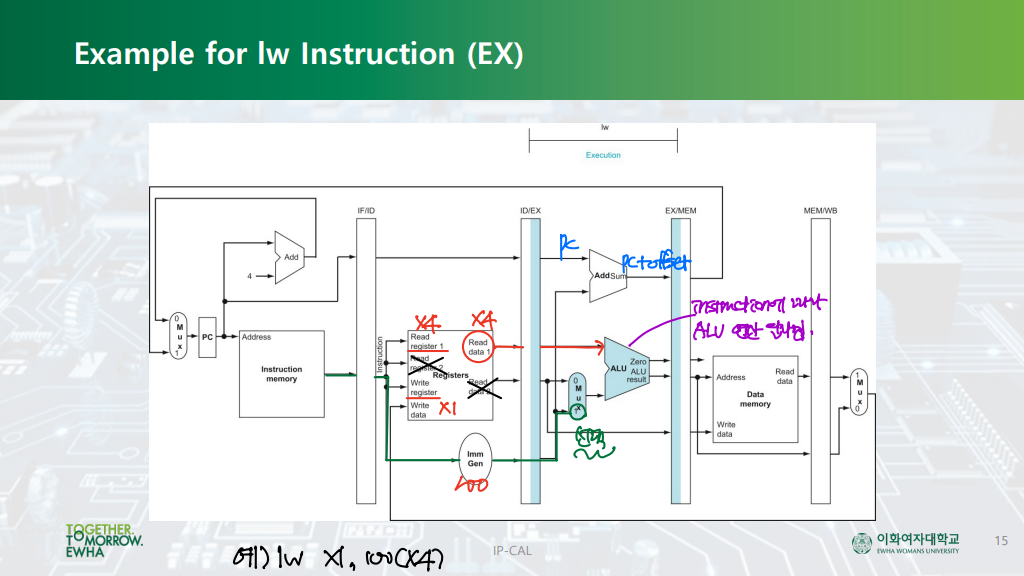

- PC

--> ID/EX pipeline register에 저장한다.

- MUX를 통해, sign-extension된 immediate 값이 ALU로 들어오도록 선택한다.

- ALU에서 add 연산을 통해, 메모리 주소를 계산한다. --> EX/MEM pipeline register에 저장한다.

Cf) Branch instruction이 아니므로, (PC+offset)을 계산할 필요는 없다.

- EX/MEM pipeline register에서 계산된 메모리 Address를 받아오고, 그 메모리 주소에 저장된 data를 읽는다.

--> MEM/WB pipeline register에 저장한다.

- MEM/WB에 저장된 Read data를 MUX에서 선택하여, Register file의 Write data에 write back한다.

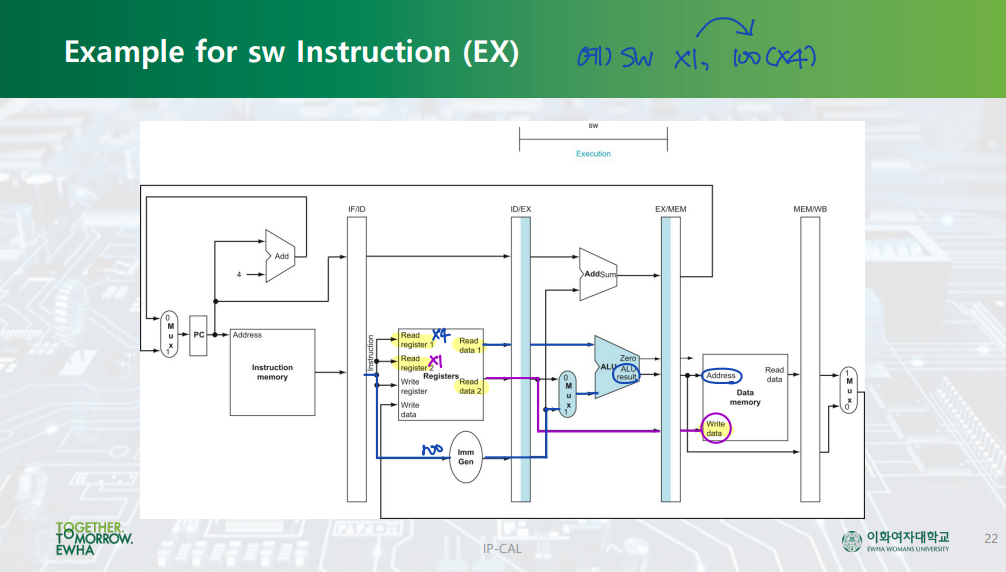

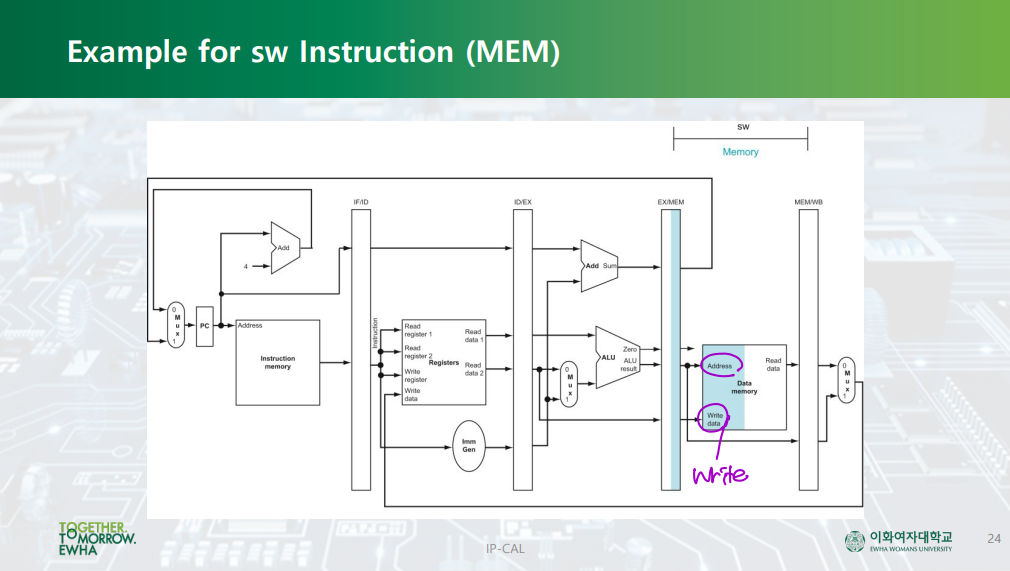

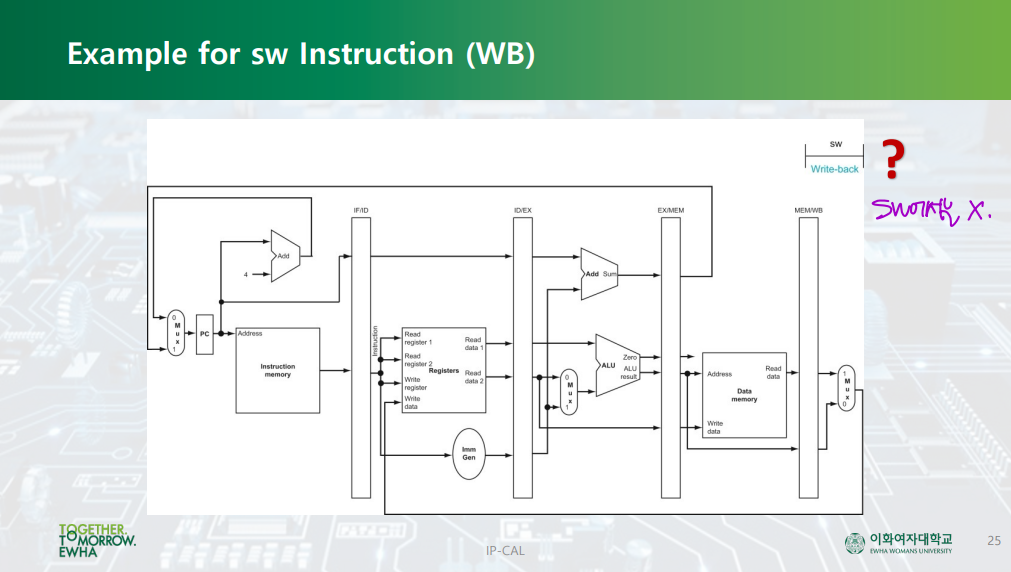

Example for sw Instruction

1. IF

2. ID

: lw와 동일하다.

- ID/EX pipeline register에 저장된 (Read data 1 + sign-extended immediate) = ALU result (메모리 주소 계산)

- ID/EX pipeline register에 저장된 Read data 2 (나중에 Write data가 됨)

--> EX/MEM에 저장한다.

- EX/MEM pipeline register에 저장된 메모리 Address값 읽어와서, 해당 메모리에 Write data를 쓴다.

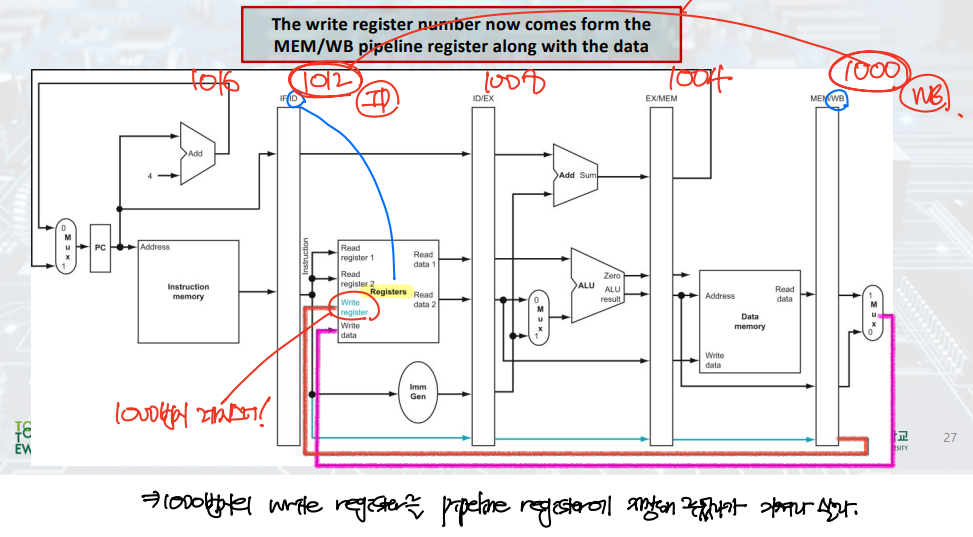

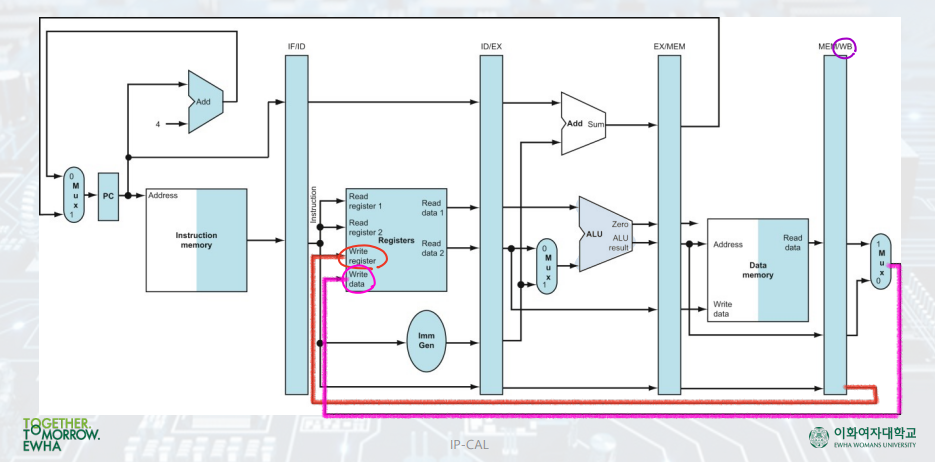

Corrected Pipelined Datapath

▷ Problem: 1000번지 instruction의 WB이 1012번지 instruction의 ID 단계와 함께 발생한다.

- ID에서의 Write register: 1012번지 instruction의 Write register인데...

- ID 단계에서의 Write data: 1000번지 instruction의 Write data이다...

▷ Solution: 1000번지 instruction의 Write register를 Pipeline register에 저장해 두었다가, 가져다 쓴다!

All Five Stages of a Load Instruction

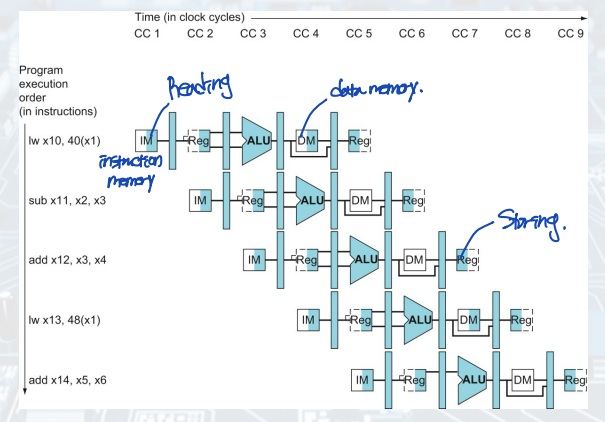

Multi-Clock-Cycle Pipeline

: 오른쪽에 색칠되면 Reading, 왼쪽에 색칠되면 Storing!

Single-Clock-Cycle Diagram (Clock Cyle 5)

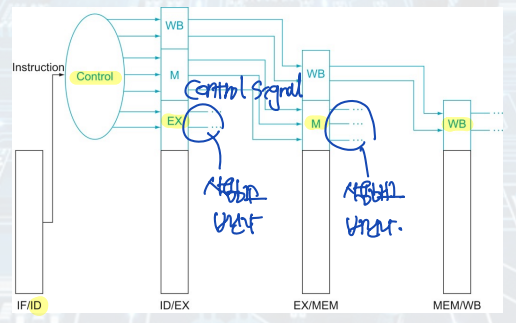

Pipelined Control

- We need only set the control values during each pipeline stage.

Pipelined Datapath with Control

Five Stages for Pipelined Control

: ID 단계에서 control signal을 생성해서, pipeline register를 통해 뒤의 단계로 전달한다.

- R-format, lw, sw, beg는 각각 control signal 값이 다르다.

Implementation of Control Signals

출처: 이화여자대학교 윤명국교수님 컴퓨터구조

'Computer Architecture > 컴퓨터구조[05]' 카테고리의 다른 글

| [CA] Lecture #22 (1) | 2023.11.17 |

|---|---|

| [CA] Lecture #21 (1) | 2023.11.15 |

| [CA] Lecture #19 (0) | 2023.11.09 |

| [CA] Lecture #18 (0) | 2023.11.08 |

| [CA] Lecture #17 (0) | 2023.11.07 |