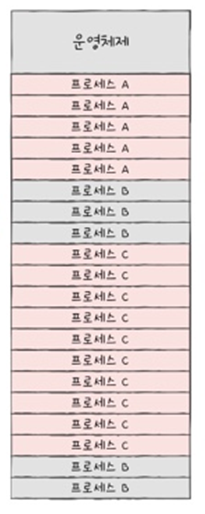

▶ 가상 메모리(virtual memory)

: 실행하고자 하는 프로그램을 일부만 메모리에 적재하여, 실제 물리 메모리 크기보다 더 큰 프로세스를 실행할 수 있게 하는 기술

- 페이징: 가상 메모리 관리 기법

페이징이란

▷ Problem - 외부 단편화

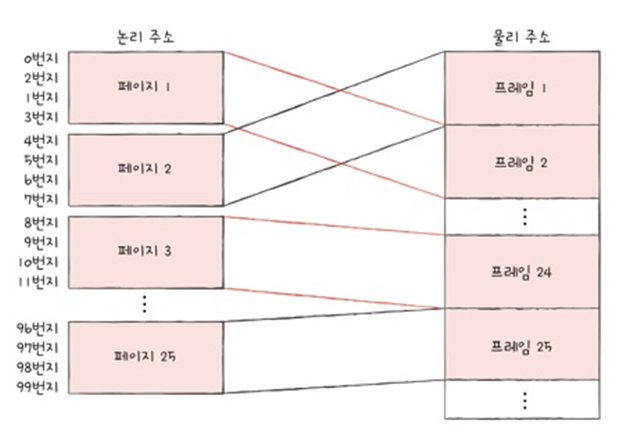

▷ Solution - 페이징

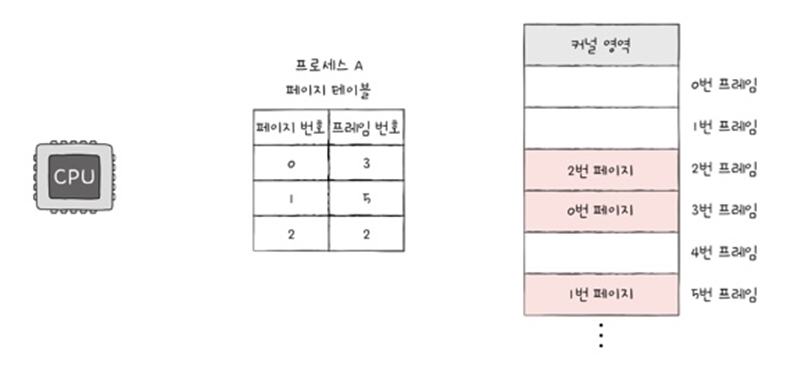

: 프로세스의 논리 주소 공간을 페이지(page)라는 단위로 자르고, 메모리 물리 주소 공간을 프레임(frame)이라는 페이지와 동일한 크기의 일정한 단위로 자른 뒤, 페이지를 프레임에 할당하는 가상 메모리 관리 기법

- 가상 메모리(논리 주소)의 page와 메인 메모리(물리 주소)의 frame을 매핑한다.

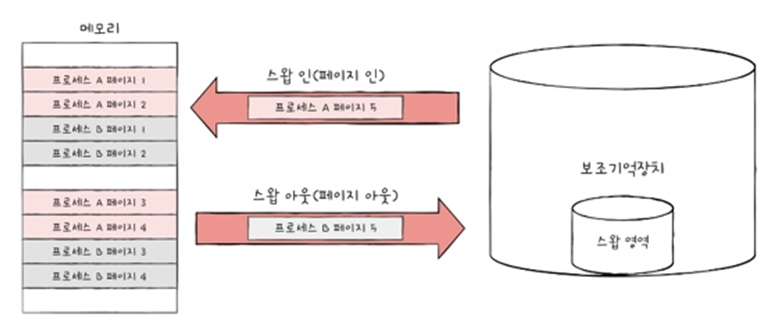

--> 페이지 단위로 swap in/swap out

- Page in: Swap in

- Page out: Swap out

▶ 가상 메모리(virtual memory)

- 메인 메모리 내 page

- Disk 내 page

--> 프로세스를 이루는 페이지 중 실행에 필요한 일부 페이지만을 메모리에 적재하고, 당장 실행에 필요하지 않은 페이지들은 보조기억장치에 남겨둘 수 있다. 이와 같은 방식을 통해 메인 메모리보다 더 큰 프로세스를 실행할 수 있다.

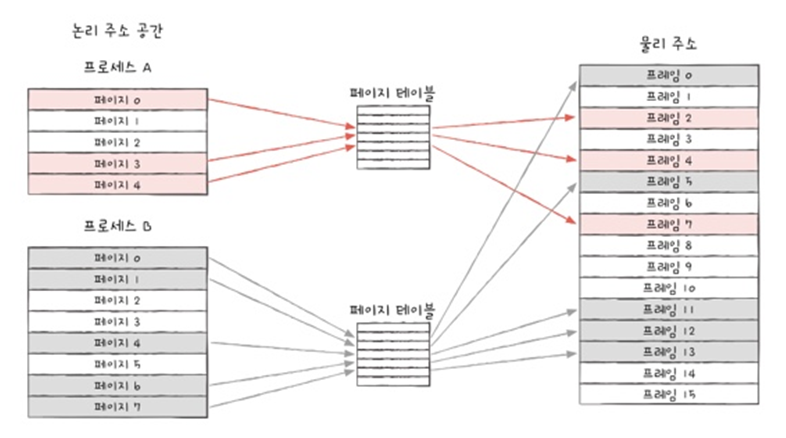

페이지 테이블

- Problem: 프로세스가 메모리에 불연속적으로 배치되어 있다면, CPU 입장에서 이를 순차적으로 실행할 수 없다.

- Solution: 페이지 테이블(page table)

▶ 페이지 테이블(page table)

: virtual memory의 page와 main memory의 frame을 매핑한다.

--> CPU 입장에서 바라본 virtual memory의 논리 주소는 연속적이기 때문에, 프로세스들이 main memory에 분산되어 저장되어 있더라도, CPU는 논리 주소를 그저 순차적으로 실행하면 된다.

: 프로세스마다 각자의 프로세스 테이블을 가지고 있고, 각 프로세스의 페이지 테이블들은 메모리에 적재되어 있다.

- 페이지 테이블 베이스 레지스터(PTBR: Page Table Base Register)

: 각 프로세스의 페이지 테이블이 적재된 주소를 가리킨다.

- Problem: 페이지 테이블을 메모리에 두면, 각 프로세스 별로 페이지 테이블을 찾을 때 main memory에 접근하고(1번), 페이지 테이블에 의거하여 main memory의 frame에 접근할 때 다시 main memory에 접근(2번)하게 된다.

- Solution: TLB(Translation Lookaside Buffer)

▶ TLB(Translation Lookaside Buffer)

: 페이지 테이블의 캐시 메모리

- TLB hit: TLB에 CPU가 발생한 virtual memory(논리 주소)에 대한 page 번호가 있을 경우, 해당 프로세스에 대한 페이지 테이블을 찾으러 main memory에 접근할 필요 없이, TLB에서 frame 번호를 받아와서 main memory에 그 frame을 찾으러 가면 된다.

- TLB miss: TLB에 CPU가 발생한 virtual memory(논리 주소)에 대한 page 번호가 없을 경우, 해당 프로세스에 대한 페이지 테이블을 찾으로 main memory에 접근해야 한다.

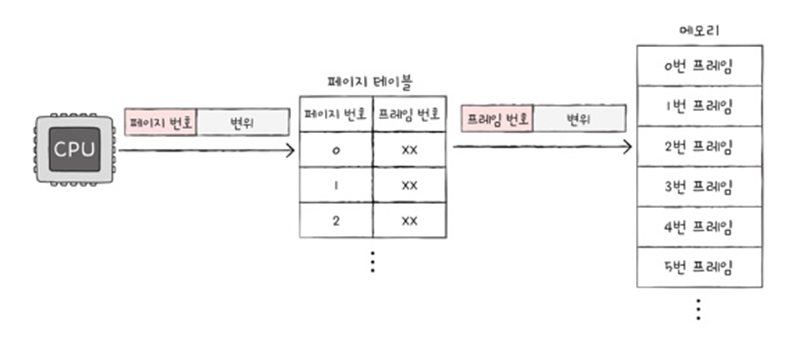

페이징에서의 주소 변환

--> 페이지 번호, 변위(offset) 필요하다.

- CPU가 virtual memory에 접근하여 page를 알아낸다.

- 알아낸 page를 들고 page table에 접근하여 main memory의 frame을 알아낸다.

- main memory의 해당 frame에 접근한다.

페이지 테이블 엔트리(PTE: Page Table Entry)

- Page 번호: virtual memory

- Frame 번호: main memory

- Valid bit: "해당 page가 main memory에 있는가?"

- 1: main memory에 있다. page 번호에 맞는 frame 번호를 보고 main memory로 가면 된다.

- 0: main memory에 없다. Disk로 간다. (페이지 폴트; page fault) - Protection bit: 해당 page가 read/write/execute 중에 무엇이 가능한지 표시한다.

- Reference bit: LRU를 위해 필요한 bit --> 해당 page가 최근에 사용된 적이 있는지 표시한다.

- 1: 최근에 사용됐다.

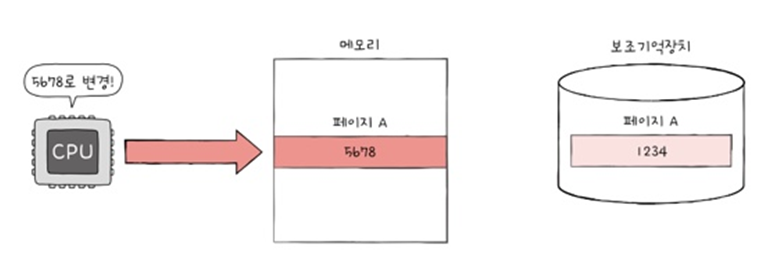

- 0: 최근에 사용되지 않았다. --> Disk로 쫓아낸다! - Dirty bit: 해당 page에 데이터를 쓴 적이 있는지 여부를 나타낸다.

- 1: 변경된 적이 있는 page

- 0: 변경된 적이 없는 page

--> 변경된 적이 있다면, 해당 page가 main memory에서 쫓겨날 때, disk에 써야 한다.

- Paging: main memory 공간을 frame 단위로 자르고, 프로세스의 virtual memory 공간을 page 단위로 자른 뒤, 각 page를 frame에 할당하는 virtual memory 관리 기법

- Page Table: page가 적재된 frame을 찾을 수 있게 한다.

- PTBR: 각 프로세스의 Page Table이 적재된 main memory 주소를 가리킨다.

- TLB: Page Table의 캐시 메모리 역할을 수행하기 위해, Page Table의 일부를 저장한다.

'Computer Architecture > 컴퓨터구조[01]' 카테고리의 다른 글

| [컴퓨터구조] 1127 (1) | 2023.11.28 |

|---|---|

| [혼자 공부하는 운영체제] 14-3. 페이지 교체와 프레임 할당 (1) | 2023.11.28 |

| [혼자 공부하는 운영체제] 14-1. 연속 메모리 할당 (0) | 2023.11.27 |

| [컴퓨터구조] 1120 (0) | 2023.11.21 |

| [컴퓨터구조] 1115 (0) | 2023.11.15 |