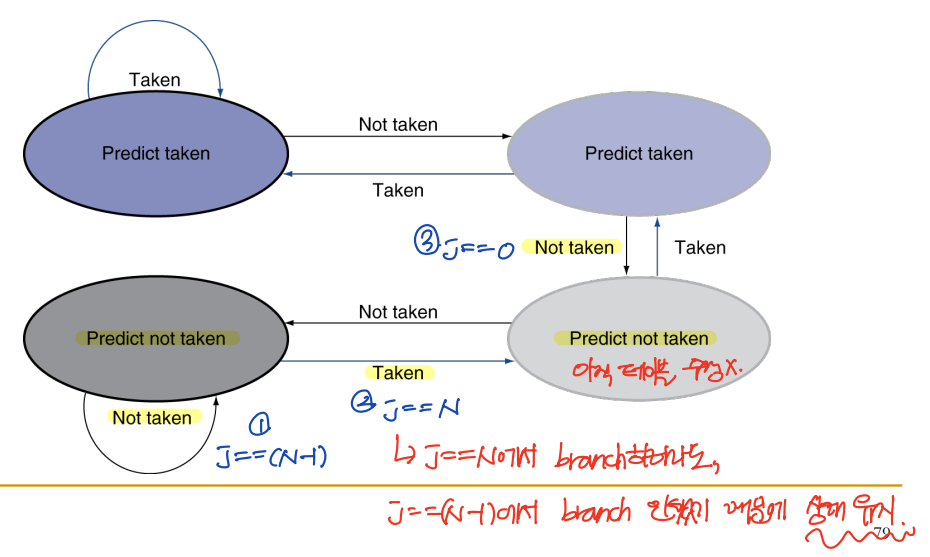

Branch Prediction

1-Bit Predictor: shortcoming

▷ Inner loop가 두 번 mispredict한다.

- j==N일 때 mispredict: branch해야 하는데 branch하지 않는 것으로 predict. (j == N-1 에서 branch하지 않았기 때문)

- j==0일 때 mispredict: branch하지 말아야 하는데 branch하는 것으로 predict. (j == N에서 branch했기 때문)

2-Bit Predictor

: Branch 여부가 한 번 바뀌었을 때는 아직 상태 유지하고, 두 번 바뀌어야 예측을 바꾼다.

Calculating the Branch Target

▷ Problem: branch할 위치는 계속 계산해야 한다.

▷ Solution: branch target buffer (branch history table)에 계산된 target address를 기록해둔다.

- 한 번의 branch instruction 수행 후에는 target address를 저장할 수 있다!

Exceptions

Exceptions & Interrupts

- Exception: Arises within the CPU.

- Interrupt: From an external I/O contorller.

Handling Exceptions

- EPC: Exception/Interrupt 당한 PC값을 저장한다.

- Cause register: Exception/Interrupt 이유를 저장한다.

- Jump to handler!

--> Handler에서 처리한 이후에, go back.

Handler Actions

- 원인을 읽고, 관련있는 handler로 보낸다.

- 필요한 action을 취한다.

- EPC를 이용해, 돌아간다. (참고로, EPC에는 PC+4 가 저장돼 있기 때문에, EPC-4 로 돌아가야 함)

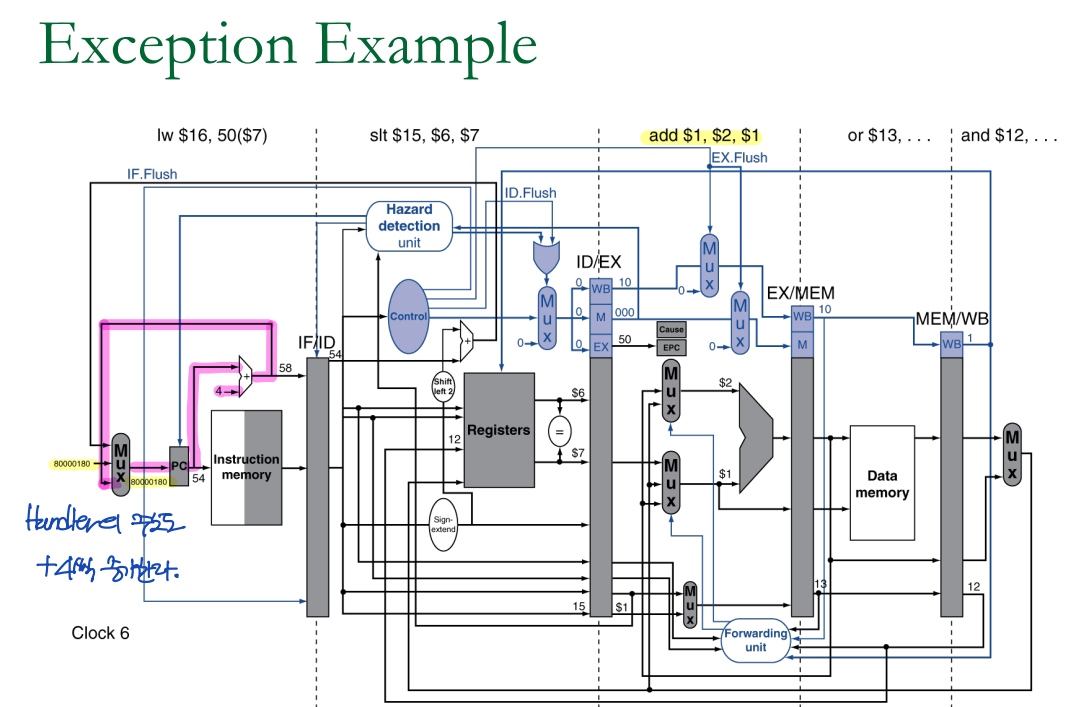

Exceptions in a Pipeline (파이프라인에서의 예외 처리)

- Prevent $1 from being clobbered. ($1을 계산하는 과정에서 오버플로우가 발생했기 때문)

- Complete previous instructions.

- Flush add and subsequent instructions.

- Set Cause register and EPC register values.

- Transfer control to handler.

Exception Properties

- 파이프라인은 instruction을 flush할 수 있다.

- Handler가 수행된 이후, EPC를 이용해 (EPC-4) 원래의 instruction으로 돌아간다.

Exception Example

Multiple Exceptions

- Simple approach: Deal with exception from the earliest instruction.

- Flush subsequent instructions.

- "Precise" exceptions.

Imprecise Exceptions (원인을 알 수 없는 Exception)

: Handler가 알아서 처리한다.

Performance

Response Time & Throughput

- Response time: How long it takes to do a task?

- Throughput: Total work done per unit time.

--> Response time으로 성능을 측정합니다!

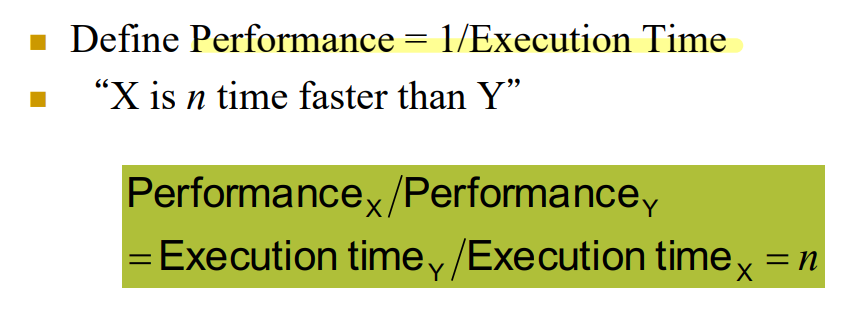

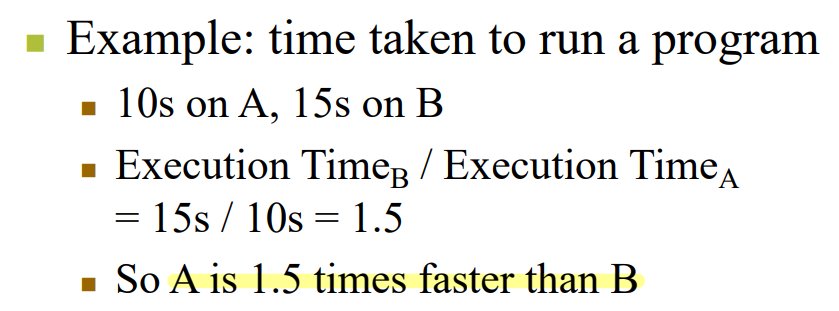

Relative Performance

Measuring Execution Time

- Elapsed time

- CPU time

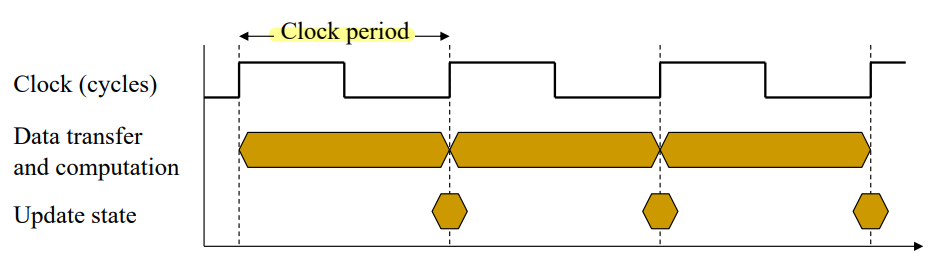

CPU Clocking

- CPU period: Duration of a clock cycle.

- Clock frequency (rate): Cycles per second. (1초에 몇 번?)

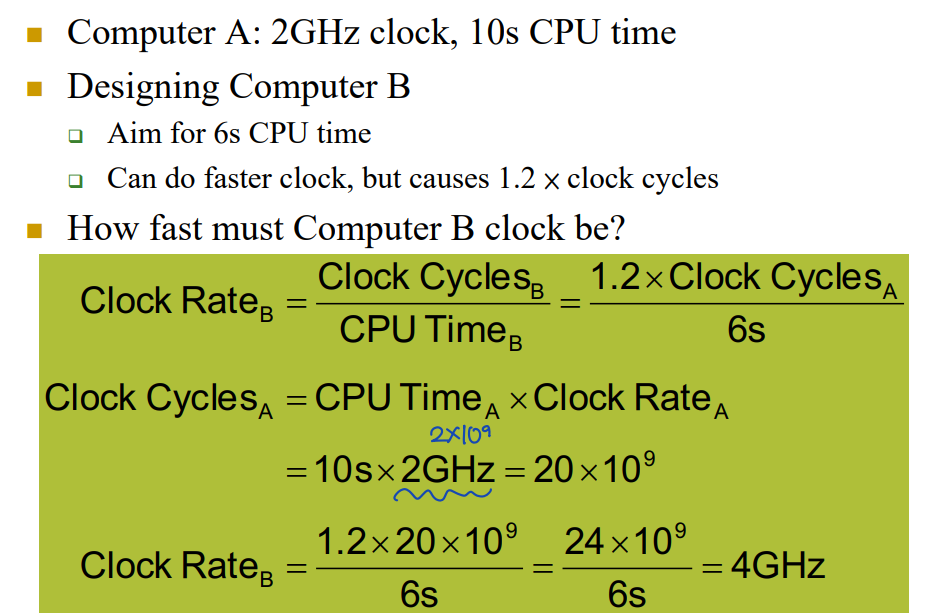

CPU Time

- CPU clock cycle을 줄여라.

- Clock rate를 높여라.

CPU Time Example

출처: 이화여자대학교 이형준교수님 컴퓨터구조

'Computer Architecture > 컴퓨터구조[01]' 카테고리의 다른 글

| [컴퓨터구조] 1113 (2) Ch5. Cache & Memory Systems (0) | 2023.11.13 |

|---|---|

| [컴퓨터구조] 1113 (1) (0) | 2023.11.13 |

| [컴퓨터구조] 1106 (0) | 2023.11.09 |

| [컴퓨터구조] 1101 (0) | 2023.11.05 |

| [컴퓨터구조] 1030 (1) | 2023.11.02 |