Data Hazard

: Data hazard는 data가 WB되기 전에 ID되면 발생한다.

- Data hazard occur when data is used before it is stored.

▶ Data hazard 종류:

- EX hazard

- MEM hazard

1) EX hazard: forwarding

: EX hazard는 1 prior result를 forwarding하면 해결할 수 있다. (No delay)

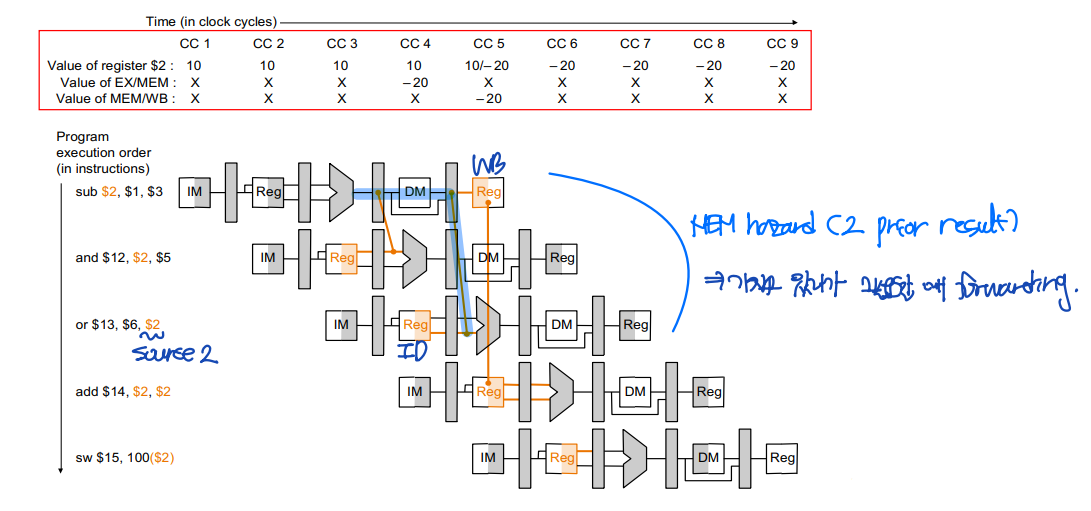

2) MEM hazard: forwarding

: MEM hazard는 2 prior result를 한 번 가지고 있다가, forwarding하면 해결할 수 있다. (No delay)

(Forwarding하지 않는 경우)

Data Hazard Solution: Forwarding

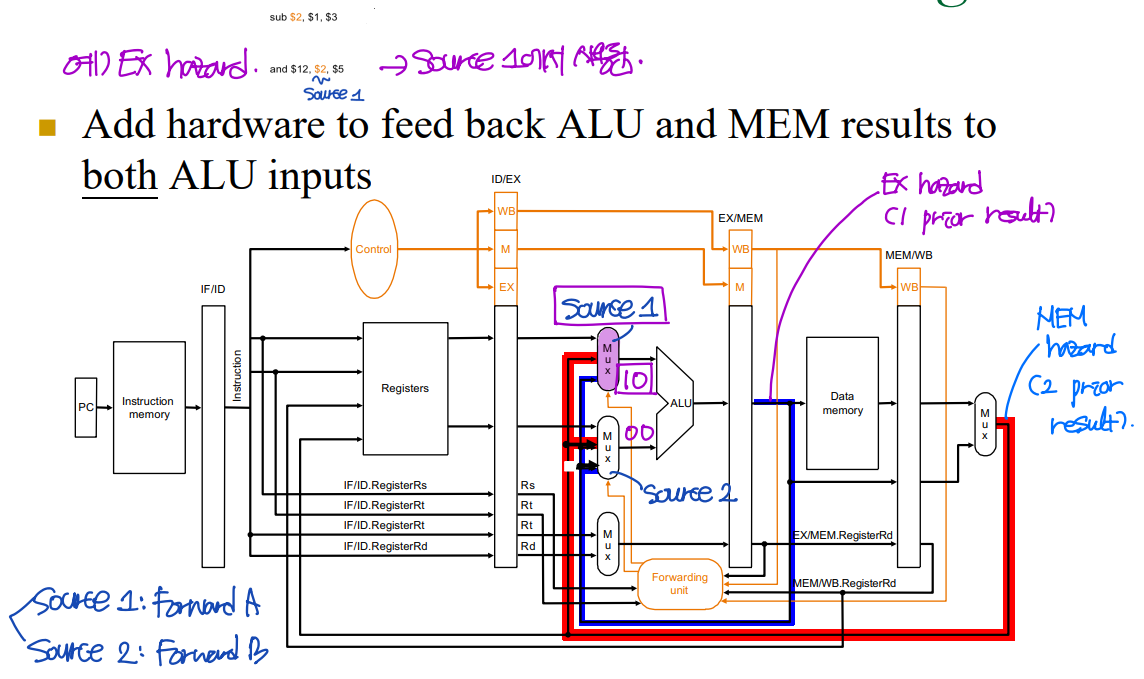

1) EX hazard

- EX hazard의 경우, ALU 다음의 pipeline register에서 forwarding한다.

- Source 1에서 사용될 경우에는 Forward A, Source 2에서 사용될 경우에는 Forward B의 MUX 값을 10으로 설정한다. (MUX의 두 번째 값 이용하기 때문: 2)

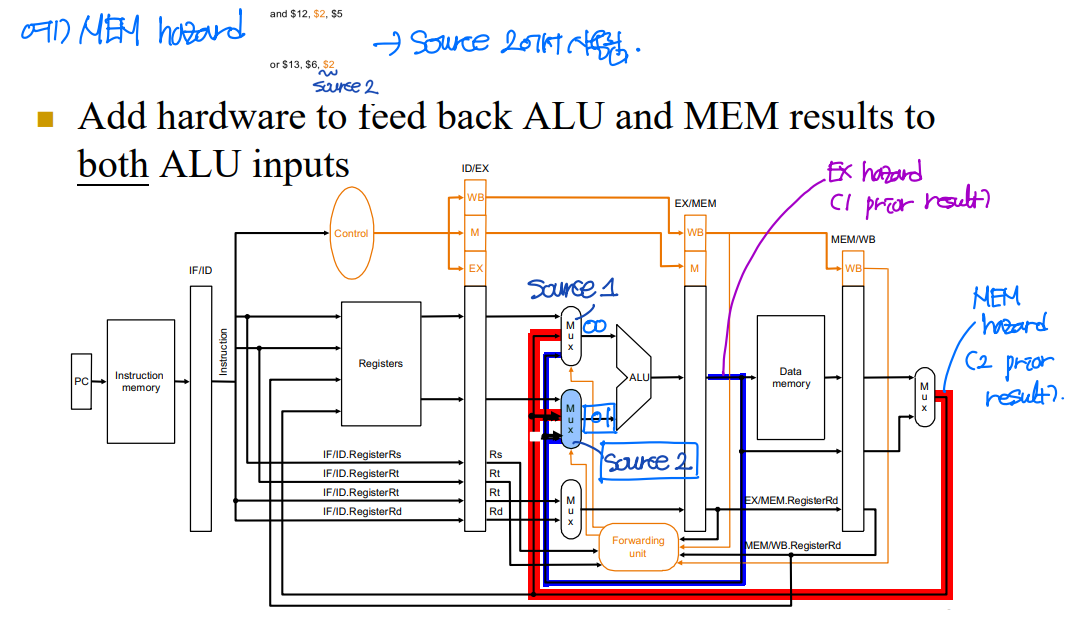

2) MEM hazard

- MEM hazard의 경우, Data Memory 다음의 pipeline register에서 forwarding한다.

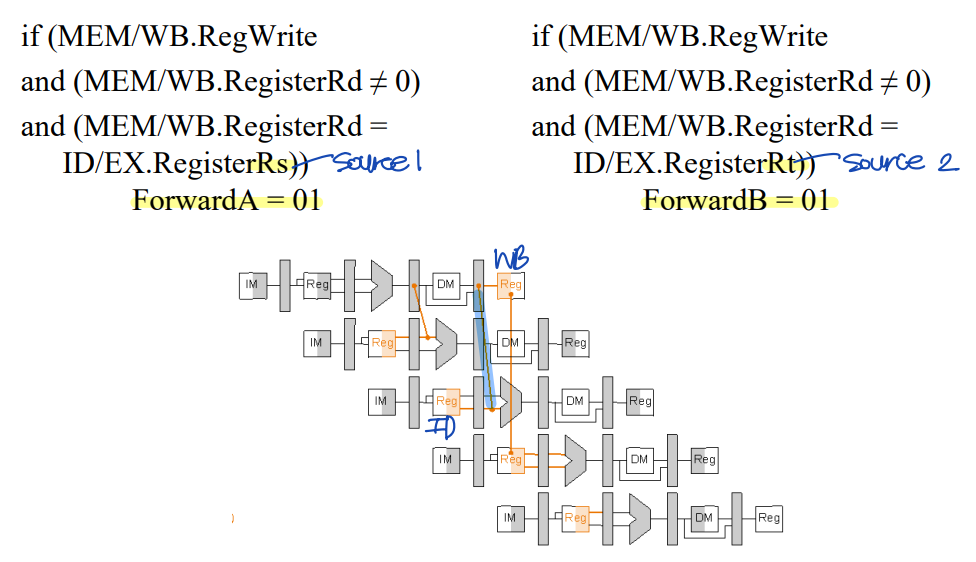

- Source 1에서 사용될 경우에는 Forward A, Source 2에서 사용될 경우에는 Forward B의 MUX 값을 01으로 설정한다. (MUX의 첫 번째 값 이용하기 때문: 1)

Forwarding Unit Detail

1) EX hazard

2) MEM hazard

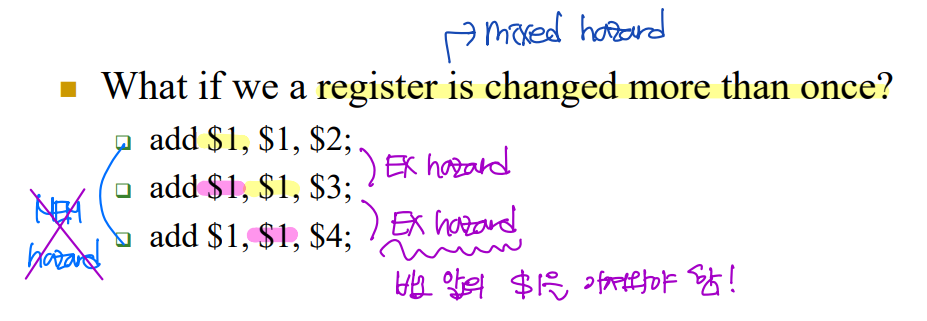

EX Hazard Complication: Mixed Hazard

: 가장 최근에 업데이트된 값을 forward한다.

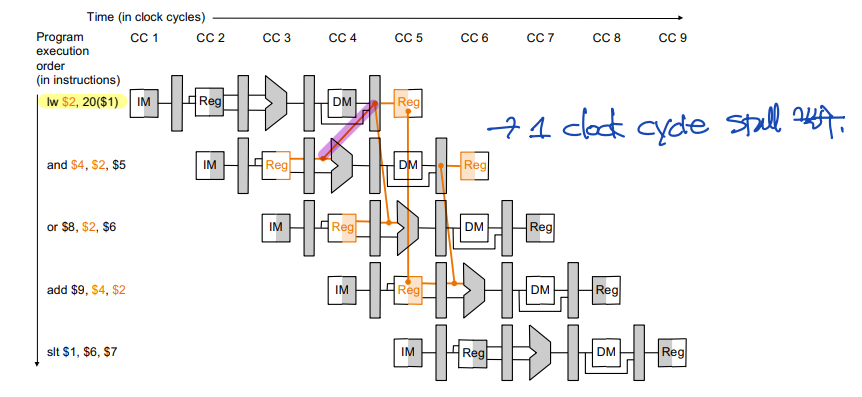

Data Hazards and Stalls: lw, sw

: lw, sw의 경우에는 MEM 단계 이후에 forward할 수 있기 때문에, 1 stall은 필수적이다.

--> 다른 상관없는 instruction을 끼워넣는다.

Pipelined Processor with Hazard Detection

Hazard Detection Unit - what happens

- MUX zeros out control signals for instruction in ID.

- "Squashes" the instruction.

- (nop) propagates through following stages. - IF/ID holds stalled instruction until the next clock cycle.

- PC holds current value until next clock cycle and re-loads first instruction.

--> nop를 이용하여 한번 stall한 후, instruction을 다시 보낸다.

Reducing Branch Delay

Branch의 경우에는 EX 단계에서 sub 연산을 통해 두 레지스터 값을 비교한 이후에야, 그 다음 instruction의 수행 여부를 결정할 수 있다.

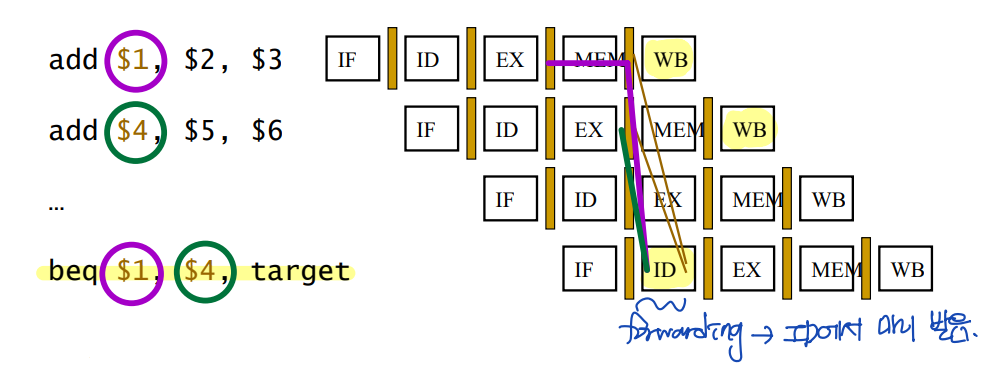

Data Hazard for Branches

Case 1) add

: Branch에서 발생하는 delay를 줄이기 위한 방법은, branch에서 비교해야 하는 레지스터 값들을 EX 단계 이전에, ID 단계에서 forwarding을 통해 미리 받아오는 것이다.

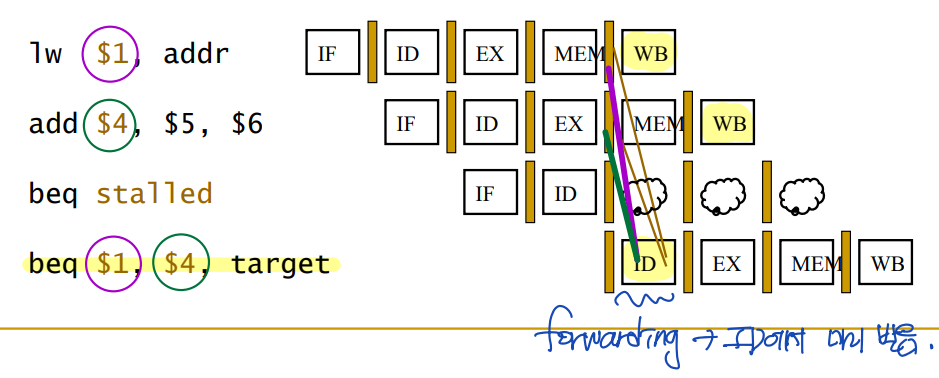

Case 2) lw

: lw가 먼저 나오는 경우, branch에서의 delay를 감소시키기 위해 forwarding을 하면 오히려 stall이 2 stall로 늘어난다.

--> 원래대로 EX 단계에서 비교를 하면, 1 stall이다.

- Control hazard - Solution 1) 레지스터 값의 비교를 EX 단계 이전에 수행하자.

--> 이 해결법 때문에 stall이 증가함... 그냥 원래대로 하자!

Control Hazard: Dynamic Branch Prediction

- Control hazard - Solution 3) Branch prediction

▶ Dynamic branch

: Branch prediction buffer (branch history table)에 이전의 branch 여부를 저장해두고, 바로 이전의 branch 여부와 똑같이 하자!

- Problem: 단지 하나의 history에만 의존함...

출처: 이화여자대학교 이형준교수님 컴퓨터구조

'Computer Architecture > 컴퓨터구조[01]' 카테고리의 다른 글

| [컴퓨터구조] 1113 (1) (0) | 2023.11.13 |

|---|---|

| [컴퓨터구조] 1108 (0) | 2023.11.09 |

| [컴퓨터구조] 1101 (0) | 2023.11.05 |

| [컴퓨터구조] 1030 (1) | 2023.11.02 |

| [컴퓨터구조] 4. The Processor (1) (0) | 2023.10.22 |